如何處理MOS管小電流發熱?

本文來源:ECCN中電網

MOSFET的擊穿有哪幾種?

Source、Drain、Gate

場效應管的三極:源級S、漏級D、柵級G

(這裏不講柵極GOX擊穿了啊,隻針對漏極電壓擊穿)

先講測試條件,都是源柵襯底都是接地,然後掃描漏極電壓,直至Drain端電流達到1uA。所以從器件結構上看,它的漏電通道有三條:Drain到source、Drain到Bulk、Drain到Gate。

1、 Drain-》Source穿通擊穿:

這個主要是Drain加反偏電壓後,使得Drain/Bulk的PN結耗盡區延展,當耗盡區碰到Source的時候,那源漏之間就不需要開啟就形成了 通路,所以叫做穿通(punch through)。那如何防止穿通呢?這就要回到二極管反偏特性了,耗盡區寬度除了與電壓有關,還與兩邊的摻雜濃度有關,濃度越高可以抑製耗盡區寬度延展,所以flow裏麵有個防穿通注入(APT:AnTI Punch Through),記住它要打和well同type的specis。當然實際遇到WAT的BV跑了而且確定是從Source端走了,可能還要看是否 PolyCD或者Spacer寬度,或者LDD_IMP問題了,那如何排除呢?這就要看你是否NMOS和PMOS都跑了?POLY CD可以通過Poly相關的WAT來驗證。對吧?

對於穿通擊穿,有以下一些特征:

(1)穿通擊穿的擊穿點軟,擊穿過程中,電流有逐步增大的特征,這是因為耗盡層擴展較寬,產生電流較大。另一方麵,耗盡層展寬大容易發生DIBL效應,使源襯底結正偏出現電流逐步增大的特征。

(2)穿通擊穿的軟擊穿點發生在源漏的耗盡層相接時,此時源端的載流子注入到耗盡層中,被耗盡層中的電場加速達到漏端,因此,穿通擊穿的電流也有急劇增大點,這個電流的急劇增大和雪崩擊穿時電流急劇增大不同,這時的電流相當於源襯底PN結正向導通時的電流,而雪崩擊穿時的電流主要為PN結反向擊穿時的雪崩電流,如不作限流,雪崩擊穿的電流要大。

(3)穿通擊穿一般不會出現破壞性擊穿。因為穿通擊穿場強沒有達到雪崩擊穿的場強,不會產生大量電子空穴對。

(4)穿通擊穿一般發生在溝道體內,溝道表麵不容易發生穿通,這主要是由於溝道注入使表麵濃度比濃度大造成,所以,對NMOS管一般都有防穿通注入。

(5)一般的,鳥嘴邊緣的濃度比溝道中間濃度大,所以穿通擊穿一般發生在溝道中間。

(6)多晶柵長度對穿通擊穿是有影響的,隨著柵長度增加,擊穿增大。而對雪崩擊穿,嚴格來說也有影響,但是沒有那麼顯著。

2、 Drain-》Bulk雪崩擊穿

這就單純是PN結雪崩擊穿了(avalanche Breakdown),主要是漏極反偏電壓下使得PN結耗盡區展寬,則反偏電場加在了PN結反偏上麵,使得電子加速撞擊晶格產生新的電子空穴對 (Electron-Hole pair),然後電子繼續撞擊,如此雪崩倍增下去導致擊穿,所以這種擊穿的電流幾乎快速增大,I-V curve幾乎垂直上去,很容燒毀的。(這點和源漏穿通擊穿不一樣)

那如何改善這個juncTIon BV呢?所以主要還是從PN結本身特性講起,肯定要降低耗盡區電場,防止碰撞產生電子空穴對,降低電壓肯定不行,那就隻能增加耗盡區寬度了,所以要改變 doping profile了,這就是為什麼突變結(Abrupt juncTIon)的擊穿電壓比緩變結(Graded JuncTIon)的低。這就是學以致用,別人雲亦雲啊。

當然除了doping profile,還有就是doping濃度,濃度越大,耗盡區寬度越窄,所以電場強度越強,那肯定就降低擊穿電壓了。而且還有個規律是擊穿電壓通常是由低 濃度的那邊濃度影響更大,因為那邊的耗盡區寬度大。公式是BV=K*(1/Na+1/Nb),從公式裏也可以看出Na和Nb濃度如果差10倍,幾乎其中一 個就可以忽略了。

那實際的process如果發現BV變小,並且確認是從junction走的,那好好查查你的Source/Drain implant了

3、 Drain-》Gate擊穿

這個主要是Drain和Gate之間的Overlap導致的柵極氧化層擊穿,這個有點類似GOX擊穿了,當然它更像 Poly finger的GOX擊穿了,所以他可能更care poly profile以及sidewall damage了。當然這個Overlap還有個問題就是GIDL,這個也會貢獻Leakage使得BV降低。

上麵講的就是MOSFET的擊穿的三個通道,通常BV的case以前兩種居多。

上麵講的都是Off-state下的擊穿,也就是Gate為0V的時候,但是有的時候Gate開啟下Drain加電壓過高也會導致擊穿的,我們稱之為 On-state擊穿。這種情況尤其喜歡發生在Gate較低電壓時,或者管子剛剛開啟時,而且幾乎都是NMOS。所以我們通常WAT也會測試BVON。

如何處理mos管小電流發熱嚴重情況?

mos管,做電源設計,或者做驅動方麵的電路,難免要用到MOS管。MOS管有很多種類,也有很多作用。做電源或者驅動的使用,當然就是用它的開關作用。

無論N型或者P型MOS管,其工作原理本質是一樣的。MOS管是由加在輸入端柵極的電壓來控製輸出端漏極的電流。MOS管是壓控器件它通過加在柵極上的電壓控製器件的特性,不會發生像三極管做開關時的因基極電流引起的電荷存儲效應,因此在開關應用中,MOS管的開關速度應該比三極管快。

我們經常看MOS管的PDF參數,MOS管製造商采用RDS(ON)參數來定義導通阻抗,對開關應用來說,RDS(ON)也是最重要的器件特性。數據手冊定義RDS(ON)與柵極(或驅動)電壓VGS以及流經開關的電流有關,但對於充分的柵極驅動,RDS(ON)是一個相對靜態參數。一直處於導通的MOS管很容易發熱。另外,慢慢升高的結溫也會導致RDS(ON)的增加。MOS管數據手冊規定了熱阻抗參數,其定義為MOS管封裝的半導體結散熱能力。RθJC的最簡單的定義是結到管殼的熱阻抗。

mos管小電流發熱的原因:

1、電路設計的問題:就是讓MOS管工作在線性的工作狀態,而不是在開關狀態。這也是導致MOS管發熱的一個原因。如果N-MOS做開關,G級電壓要比電源高幾V,才能完全導通,P-MOS則相反。沒有完全打開而壓降過大造成功率消耗,等效直流阻抗比較大,壓降增大,所以U*I也增大,損耗就意味著發熱。這是設計電路的最忌諱的錯誤。

2、頻率太高:主要是有時過分追求體積,導致頻率提高,MOS管上的損耗增大了,所以發熱也加大了。

3、沒有做好足夠的散熱設計:電流太高,MOS管標稱的電流值,一般需要良好的散熱才能達到。所以ID小於最大電流,也可能發熱嚴重,需要足夠的輔助散熱片。

4、MOS管的選型有誤:對功率判斷有誤,MOS管內阻沒有充分考慮,導致開關阻抗增大。

mos管小電流發熱嚴重怎麼解決:

1、做好MOS管的散熱設計,添加足夠多的輔助散熱片。

2、貼散熱膠。

MOS管為什麼可以防止電源反接?

電源反接,會給電路造成損壞,不過,電源反接是不可避免的。所以,我們就需要給電路中加入保護電路,達到即使接反電源,也不會損壞的目的。

一般可以使用在電源的正極串入一個二極管解決,不過,由於二極管有壓降,會給電路造成不必要的損耗,尤其是電池供電場合,本來電池電壓就3.7V,你就用二極管降了0.6V,使得電池使用時間大減。

MOS管防反接,好處就是壓降小,小到幾乎可以忽略不計。現在的MOS管可以做到幾個毫歐的內阻,假設是6.5毫歐,通過的電流為1A(這個電流已經很大了),在他上麵的壓降隻有6.5毫伏。

由於MOS管越來越便宜,所以人們逐漸開始使用MOS管防電源反接了。

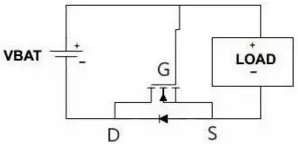

① NMOS管防止電源反接電路:

正確連接時:剛上電,MOS管的寄生二極管導通,所以S的電位大概就是0.6V,而G極的電位,是VBAT,VBAT-0.6V大於UGS的閥值開啟電壓,MOS管的DS就會導通,由於內阻很小,所以就把寄生二極管短路了,壓降幾乎為0。

電源接反時:UGS=0,MOS管不會導通,和負載的回路就是斷的,從而保證電路安全。

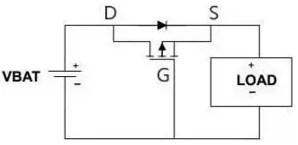

② PMOS管防止電源反接電路:

正確連接時:剛上電,MOS管的寄生二極管導通,電源與負載形成回路,所以S極電位就是VBAT-0.6V,而G極電位是0V,PMOS管導通,從D流向S的電流把二極管短路。

電源接反時:G極是高電平,PMOS管不導通。保護電路安全。

連接技巧

NMOS管DS串到負極,PMOS管DS串到正極,讓寄生二極管方向朝向正確連接的電流方向。

感覺DS流向是“反”的?

仔細的朋友會發現,防反接電路中,DS的電流流向,和我們平時使用的電流方向是反的。

為什麼要接成反的?

利用寄生二極管的導通作用,在剛上電時,使得UGS滿足閥值要求。

為什麼可以接成反的?

如果是三極管,NPN的電流方向隻能是C到E,PNP的電流方向隻能是E到C。不過,MOS管的D和S是可以互換的。這也是三極管和MOS管的區別之一。

MOS管功率損耗測量

MOSFET/IGBT的開關損耗測試是電源調試中非常關鍵的環節,但很多工程師對開關損耗的測量還停留在人工計算的感性認知上,PFC MOSFET的開關損耗更是隻能依據口口相傳的經驗反複摸索,那麼該如何量化評估呢?

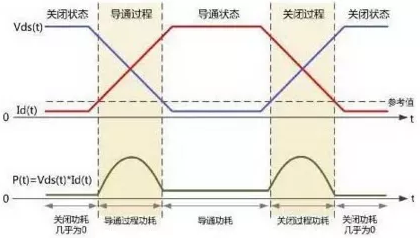

1、功率損耗的原理圖和實測圖

一般來說,開關管工作的功率損耗原理圖如圖 1所示,主要的能量損耗體現在“導通過程”和“關閉過程”,小部分能量體現在“導通狀態”,而關閉狀態的損耗很小幾乎為0,可以忽略不計。

實際的測量波形圖一般如圖 2所示:

2、MOSFET和PFC MOSFET的測試區別

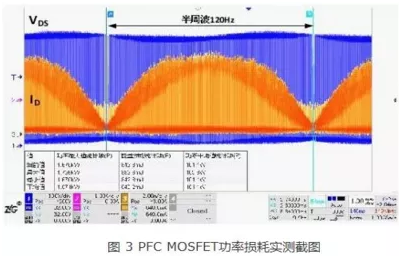

對於普通MOS管來說,不同周期的電壓和電流波形幾乎完全相同,因此整體功率損耗隻需要任意測量一個周期即可。但對於PFC MOS管來說,不同周期的電壓和電流波形都不相同,因此功率損耗的準確評估依賴較長時間(一般大於10ms),較高采樣率(推薦1G采樣率)的波形捕獲,此時需要的存儲深度推薦在10M以上,並且要求所有原始數據(不能抽樣)都要參與功率損耗計算,實測截圖如圖 3所示。

聲明:本網站原創內容,如需轉載,請注明出處;本網站轉載的內容(文章、圖片、視頻)等資料版權歸原網站所有。如我們采用了您不宜公開的文章或圖片,未能及時和您確認,避免給雙方造成不必要的經濟損失,請電郵聯係我們,以便迅速采取適當處理措施;郵箱:[email protected]